Семейство

микроконтроллеров MCS-51 включает в

себя значительный ряд микросхем от простых до сложных. Цены на данное семейство

умеренные, например микроконтроллер AT89C2051 можно купить за 1$. Данные микросхемы позволяют

реализовать все функции микроЭВМ. Так же все микроконтроллеры семейства MCS-51

работают с одной системой команд и выполнены в одинаковых корпусах, с

совпадающей нумерацией ножек. Все это позволяет использовать микросхемы разных

производителей (таких как Intel, Dallas, Atmel, Philips и т.д.). В

состав однокристального МК входит 8-разрядный ЦП, управляющее ПЗУ объемом 4

Кбайта, внутреннее ОЗУ объемом 128 байт, четыре двунаправленных побитно

настраиваемых восьмиразрядных порта ввода-вывода, четыре тестируемых входа,

канал последовательного ввода-вывода, два

или три 16-разрядных таймера-счетчика, две линии запросов на прерывание

от внешних устройств. Эти средства образуют резидентную часть МК, размещенную

непосредственно на кристалле. Двусторонний обмен осуществляется с помощью внутренней

8-разрядной магистрали данных, которая связывает между собой основные узлы и

устройства микроконтроллера. Базовая организация предоставляет встроенные средства

расширения своих ресурсов. Размер ПЗУ может быть увеличен до 64 кБайт за счет

подключения внешнего ПЗУ. Также, в дополнении к имеющемуся внутреннему ОЗУ,

может быть подключено внешнее ОЗУ объемом до 64 кБайт. Вся серия семейства имеет

гарвардскую архитектуру, то есть раздельные адресные пространства памяти

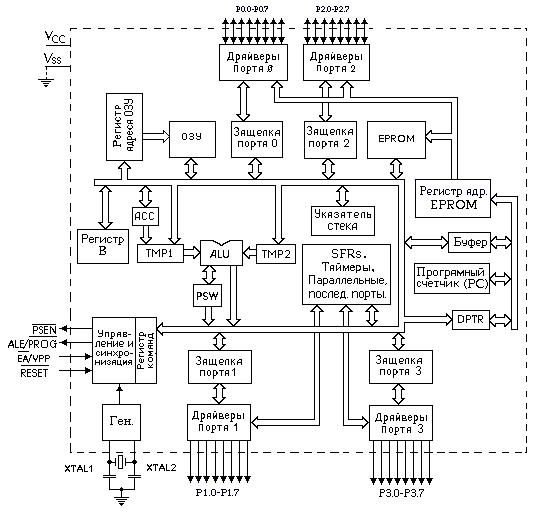

программ и данных. Структурная схема микроконтроллера представлена на рисунке 1.

Рис. 1. Структурная схема микроконтроллера Арифметико-логическое

устройство (ALU) - это параллельное восьми разрядное устройство, выполняющее

различные арифметические операции, такие как сложение, вычитание, умножение и

деление; операции логического И, ИЛИ, исключающего ИЛИ, операции сброса,

инвертирования, а так же операции циклического сдвига и др. К входам АЛУ

подключены программно-недоступные регистры T1 и T2. Они предназначены для

временного хранения операндов, схема десятичной коррекции (DCU) и схема

формирования признаков результата операции (PSW). Простейшая операция сложения

используется в АЛУ для инкрементирования содержимого регистров, продвижения

регистра-указателя данных (RAR) и автоматического вычисления следующего адреса

резидентной памяти программ. Простейшая операция вычитания используется в АЛУ

для декрементирования регистров и сравнения переменных. В АЛУ реализуется

механизм каскадного выполнения простейших операций для реализации сложных

команд. Все перечисленные операции выполняются всего лишь за 2 мкс. АЛУ может

оперировать как байтами, так и отдельными битами. Есть отдельные биты, которые

доступны пользователю. Они могут быть сброшены, установлены, проверены,

переданы, инвертированы, с ними можно выполнить логические операции. Так же АЛУ

может оперировать цифровыми (4 бита) и адресными (16 бит) типами информационных

объектов. В АЛУ выполняется 51 различная операция, используется 11 режимов

адресации (4 для адресов и 7 для данных), путем комбинирования операции и

режима адресации базовое число команд 111 увеличивается до 255. Аккумулятор

(АСС или А) – главный регистр МК, является источником исходных операндов и

приёмником результата при выполнении ряда операций. Микроконтроллер также имеет

регистр расширитель аккумулятора B, использующийся при выполнении операций

умножения и деления, либо как регистр, определяемый пользователем. Блок

управления и синхронизации управляет работой микроконтроллера, обеспечивает

взаимодействие и координацию работы всех его узлов. Также обеспечивает

функционирование микроконтроллера в двух специальных режимах: режиме холостого

хода и режиме микропотребления. В состав блока управления входят: устройство

формирования временных интервалов, логика ввода-вывода, регистр команд, регистр

управления потреблением электроэнергии, дешифратор команд, логика управления

ЭВМ. Частота

внутреннего тактового генератора определяется подключенным к выводам X1 и X2

кварцевым резонатором (типичное значение f=12-24МГц). Некоторые из современных

МК имеют встроенный умножитель внешней тактовой частоты с системой фазовой

автоподстройки частоты (ФАПЧ), что позволяет применять дешёвые низкочастотные

резонаторы, например, с частотой 32768 Гц, применяемые в генераторах часов

реального времени. Так же допускается использование в качестве частотозадающей

цепи LC-цепочку. В этом случае частота опорного синхросигнала определяется

выражением:  где f – частота генератора, L – индуктивность катушки, C – ёмкость

конденсатора.

Возможно

использование внешнего тактового генератора, его выход подключается к входу X1,

а вывод X2 подключается к общей шине. Блок

портов ввода-вывода содержит четыре 8-разрядных двунаправленных порта

ввода-вывода. Каждый порт имеет буферный регистр. Из этого регистра считываются

данные при вводе информации и записываются в регистр при выводе. Так же есть управляющий

регистр, определяющий направление передачи данных и режим использования выводов

порта — по прямому назначению или для реализации альтернативной функции

ввода-вывода (обращение к внешней памяти). К каждому отдельному разряду

параллельного порта возможно непосредственное обращение и настройка на

соответствующий режим работы.

|